Bài toán gấp đôi tờ giấy

Từ khi chíp siêu quy mô (VLSI) ra đời ở thập niên 1980, sự phát triển của chíp vi mạch đã và hiện vẫn được theo đuổi là “gia tăng độ tích hợp”; nói nôm na là tăng số transistor MOSFET trên 1 chíp: Số transistor tăng có nghĩa là chip có thể làm được nhiều việc hơn, có thể được sử dụng cho nhiều ứng dụng, nhiều mục đích hơn. Một chip ngày nay có thể có tới trên 2,5 tỷ transistor!

Bài toán hình dung vấn đề này khá đơn giản. Hãy tưởng tượng ta có một tờ giấy hình chữ nhật, hay hình vuông. Nếu ta gấp tờ giấy lại sao cho mỗi cạnh nhỏ lại bằng nửa cạnh của tờ giấy ban đầu, thì ta được 4 mảnh giấy nhỏ có hình “đồng dạng” với tờ giấy nguyên thủy. Nay nếu mỗi tờ giấy được coi là một con chíp vi mạch, khi mỗi thành tố trên chip được thu nhỏ kích thước hai chiều lại bằng 1/2, thì ta sẽ được 4 con chíp hoàn toàn đồng dạng với chíp nguyên gốc. Không những thế, vì nhỏ đi nên năng lượng tiêu thụ của mỗi chip ít đi; ngược lại tốc độ xử lý tín hiệu của chip sẽ tăng lên vì cự ly truyền dẫn của các hạt tải điện đã ngắn đi một nửa và những thành phần “ký sinh” (cảm kháng, dung kháng…) đều giảm nhờ kích thước nhỏ lại. Đây là nội dung của “Luật Moore” - một quy luật kinh nghiệm của thời kỳ công nghệ chế tạo tiến bộ chủ yếu nhờ thu nhỏ đường kẻ thiết kế: “Số transistor trên đơn vị diện tích sẽ tăng gấp đôi sau mỗi 24 tháng”.

Sự tăng trưởng về độ tích hợp của chíp vi mạch trong 40 năm (1971-2011) quả thật là đã theo gần đúng Luật Moore. Tuy nhiên, kể từ những năm 2005-2007 trở đi, độ tích hợp đã có xu hướng không còn đúng với Luật Moore nữa.

Quy trình chế tạo chip vi mạch

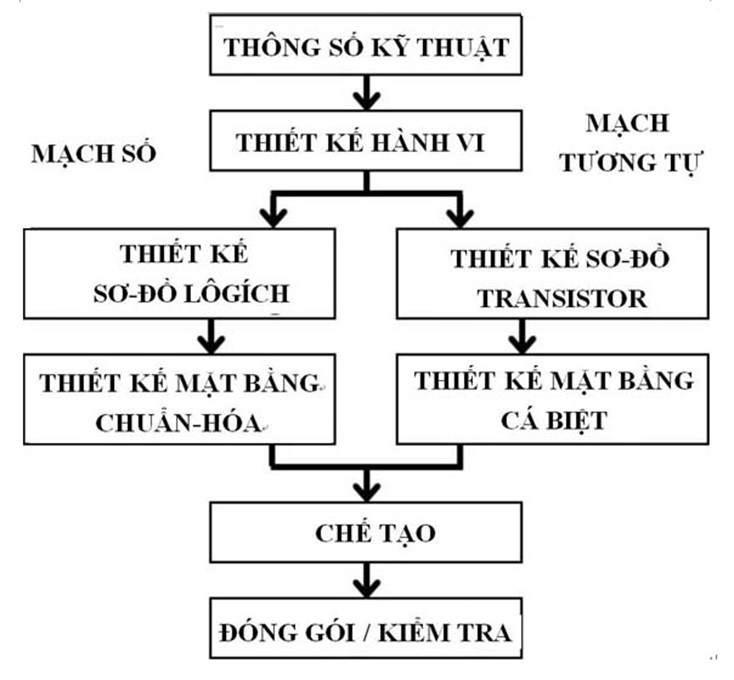

Hình 1 tóm tắt quy trình làm ra một chip vi mạch, từ thiết kế, chế tạo tới kiểm tra và đóng gói. Hình này đặc biệt chú trọng tới những công đoạn chủ yếu trong quy trình thiết kế cho tới khi bản thiết kế được chuyển giao cho chế tạo, rồi sau đó là đóng gói và kiểm tra.

Trong thiết kế, sau định nghĩa thông số, tức là quy định những tính năng của chíp và thiết kế hành vi, tức là quy định phương cách sử dụng để quyết định thực hiện chíp bằng mạch số (digital chip) hay mạch tương tự (analog chip). Mỗi công đoạn đều gồm nhiều công đoạn nhỏ, mà ở đây, để đơn giản hóa chúng ta đã lược bỏ đi.

Công đoạn chế tạo lại chia ra làm 2 phần: quy trình đầu ngọn (Front-End Pprocess) và quy trình đầu cuối (Back-End Process). Quy trình đầu ngọn chủ yếu là chế biến đĩa silicon (Si wafer). Quy trình đầu cuối là xẻ đĩa (dicing) thành chíp thô (die) và kiểm tra (test).

Công đoạn đóng gói chủ yếu biến chíp thô (die) ra thành phẩm (end product).

Đại diện cho cả bốn công đoạn (thiết kế, quy trình đầu ngọn, quy trình đầu cuối và đóng gói – kiểm tra) là những nhà sản xuất gọi là IDM (Integrated Device Manufacturer) như Intel, Samsung, Renesas...

Đại diện cho thiết kế là Qualcomm và hầu hết các công ty thiết kế vi mạch hiện đang hoạt động ở Việt Nam.

Đại diện cho chế tạo là Công ty TSMC.

Đại diện cho quy trình đầu cuối và đóng gói là Công ty Intel Việt Nam.

Hình 1. Quy trình chế tạo chip vi mạch từ thiết kế cho đến thành phẩm.

Hình 2 cho thấy rõ hơn sự phân công và quan hệ giữa các doanh nghiệp từ thiết kế, đến chế tạo thiết bị, nguyên vật liệu và hóa chất với các doanh nghiệp sản xuất chip và đóng gói chip cho tới khi chip ra tới thị trường, có thể là ở dạng chip đã đóng gói hoặc ở dạng thành phẩm.

Hình 2. Phân công và quan hệ giữa các công ty trong sản xuất vi mạch [1].

Ở hình 2, Qualcomm đảm nhiệm thiết kế một sản phẩm cho Apple. Thiết kế đó được giao cho Intel đảm nhiệm công đoạn đầu ngọn. Để làm được công đoạn đầu ngọn này, Intel cần đến vật liệu và hóa chất do Shin-Etsu cung ứng, đồng thời những thiết bị chế tạo do các công ty sản xuất thiết bị cung cấp (ASML, SCREEN...). Công đoạn đầu cuối cũng do Intel đảm nhiệm với những thiết bị mua của những công ty khác (ADVANTEST…). Giai đoạn đóng gói thành phẩm do nhiều đơn vị khác nhau chia xẻ (đại diện như PEGATRON, Panasonic....).

Cho đến nay, trong bốn công đoạn kể trên, thiết kế và quy trình đầu ngọn là hai công đoạn đòi hỏi công nghệ cao, kỹ năng cao và sự sáng tạo. Đây cũng là những công đoạn tốn tiền hơn cả. Tiến bộ của công nghệ vi mạch cho đến nay chủ yếu tập trung vào hai công đoạn này do chúng được ưu tiên đầu tư cả về tiền bạc và nhân lực. Còn quy trình đầu cuối thường bị coi nhẹ.

Công nghệ đóng gói: Vai chính của cuộc chơi trong tương lai?

Quy trình chế tạo chip đã đạt tới giới hạn? Câu hỏi này đang được đặt ra khi mà thực tế cho thấy, mặc dù chip có cấu trúc 3 nm đã được chế tạo thành công từ năm 2006, song cho tới nay (tức là 16 năm sau), người ta chỉ chế tạo đại trà chip 4 nm. Điều đó cho thấy, công nghệ thu nhỏ kích thước thiết kế đã tiến dần tới giới hạn, nếu tiếp tục đẩy xa nữa, công nghệ này trở nên quá tốn kém, khó sinh lợi nhuận.

Gần đây, trên Youtube có lưu hành một video clip tựa là “Từ nay vai chính sẽ là đóng gói chip” [1] của một youtuber khá nổi tiếng có biệt danh là Monozukuri-Taro. Trong clip này có một ý nói rằng: địa vị thấp kém của “đóng gói” từ trước đến nay trong chuỗi công đoạn sản xuất chip vi mạch sẽ thay đổi. Điều gì đã khiến người ta “võ đoán” như vậy? Ý tưởng này đã được diễn tả ngắn gọn và dễ hiểu bởi một chuyên gia vi mạch - bà Lisa Su (tên Hán Việt là Tô Tư Phong, sinh ngày 7/11/1969, Chủ tịch kiêm Tổng giám đốc điều hành Công ty AMD - Advanced Micro Devices, Mỹ).

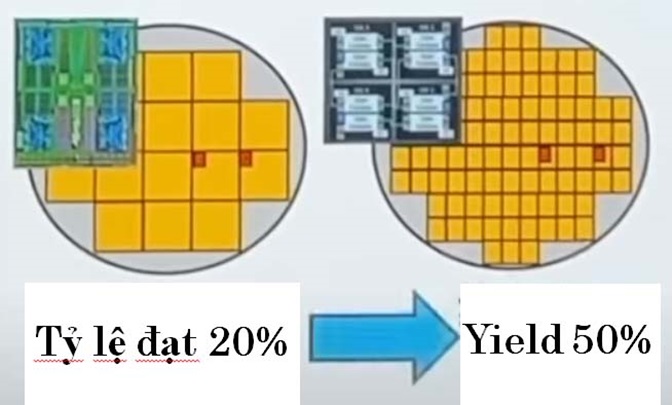

Sáng kiến của bà Lisa Su, hay nói đúng ra là “tư duy đảo ngược” của bà có thể tóm tắt như hình 3. Ở hình 3, chúng ta thấy, nửa bên trái có con chip lớn. Khi chế tạo những chip lớn như vậy thì mỗi đĩa silicon sẽ chỉ cho một số ít chip mà thôi. Nếu xảy ra vấn đề như như khuyết tật (defects) của đĩa silicon hoặc có hạt bụi dính vào thì tỷ lệ đạt (yield) sẽ thấp, chẳng hạn 20%. Nay nếu chia chip lớn ra làm 4 mảnh chíp (gọi là chiplet,) như nửa bên phải, thì những khuyết điểm vừa kể sẽ chỉ làm hư 2 mảnh nhỏ chứ không làm mất đi 2 con chip tức 8 mảnh nhỏ! Như vậy, tỷ lệ đạt có thể lên tới 50%.

Hình 3. Năng cao tỷ lệ đạt bằng chiplet.

Vì công đoạn đầu ngọn tốn nhiều tiền nên việc gia tăng tỷ lệ đạt bằng cách chế tạo chiplet chứ không chế tạo cả con chíp có thể giúp giảm giá thành đáng kể. Chính khi đó, khâu đóng gói sẽ “đăng đàn” giải quyết vấn đề. Đóng gói trong thời đại chiplet chính là phải tạo dựng lại được con chíp như thiết kế ban đầu, chứ không đơn thuần chỉ là xử lý sao cho chíp có thể kết nối được với ngoại biên như thời kỳ đóng gói con chíp hoàn chỉnh. Đây chính là lý do tại sao nói: “đóng gói” sẽ đóng “vai chính”.

Việt Nam nên tập trung vào công đoạn nào?

Hình 4. Cắt băng khánh thành Trung tâm Thiết kế vi mạch, Khu Công nghệ cao TP Hồ Chí Minh (SCDC).

Vi mạch ngày nay đã trở thành sản phẩm chiến lược. Vi mạch không chỉ là sản phẩm công nghệ cao, mà thực sự đã trở thành linh kiện chủ chốt cho mọi sản phẩm công nghiệp, từ dân dụng (điện thoại thông minh, máy vi tính....) tới quân sự.

Hãy điểm lại mấy sự kiện gần đây để có thể thấy công nghệ chế tạo chip ngày nay đã có vị trí chiến lược như thế nào:

1) Ngày 1/7/2019, Bộ Kinh tế, Thương mại và Công nghiệp Nhật Bản (METI) đã chính thức loại Hàn Quốc ra khỏi Danh sách Quốc gia trắng (White Country List). Quốc gia trắng là nước được mua mọi sản phẩm công nghiệp, kể cả sản phẩm chiến lược, của Nhật Bản không hạn chế số lượng và không phải trình báo chi tiết sử dụng thế nào. Trong những sản phẩm chiến lược này, phải kể đến những sản phẩm vô cùng quan trọng đối với quy trình chế tạo vi mạch, như các chất: cản quang, polyimide, Hydrofluoride... Hàn Quốc lệ thuộc vào Nhật Bản tới 90% về những sản phẩm chiến lược này (theo số liệu 5 tháng đầu năm 2019). Bị loại ra khỏi danh sách Quốc gia trắng không có nghĩa là bị cấm mua. Quốc gia bị loại vẫn mua được sản phẩm chiến lược của Nhật Bản, nhưng mỗi lần đặt mua sẽ phải chờ xem xét để được chấp thuận, với thời gian chờ đợi có thể lên tới 90 ngày [2].

2) Khi Tổng thống Mỹ Joe Biden tới Hàn Quốc và Nhật Bản hồi tháng 5/2022, ông có đề cập đến “Liên minh Chip 4” (Chip 4 Alliance) nhằm củng cố chuỗi cung ứng vi mạch. Ai cũng nghĩ rằng 4 ở đây gồm: Mỹ, Nhật, Đài Loan và Hàn Quốc. Mỹ, Nhật Bản và Đài Loan thì có lẽ đúng, nhưng Hàn Quốc thì sao? Hàn Quốc lệ thuộc nhiều vào Trung Quốc, từ vật liệu, nhân công cho nhà máy vi mạch đặt ở Trung Quốc. Thị trường tiêu thụ sản phẩm vi mạch của Hàn Quốc cũng chủ yếu là Trung Quốc. Do đó, Hàn Quốc không dễ gì có thể quyết định tham gia Liên minh Chip 4 [3]. Đồng thời, Trung Quốc cũng đã có động thái khiến Hàn Quốc khó có thể quyết định gia nhập Liên minh Chip 4 [4].

3) Gần đây, người ta thấy vai trò của Ấn Độ ngày càng nổi trội. Chẳng hạn, Ấn Độ được dự đoán sẽ trở thành nền kinh tế lớn thứ 3 thế giới vào năm 2030 [5]. Một số nhà máy vi mạch của Hàn Quốc khi rút khỏi Trung Quốc đã được chuyển sang Ấn Độ [6]. Ấn Độ sắp trở thành quốc gia có dân số lớn nhất (1,5 tỷ), nghĩa là có thị trường rất lớn. Quốc gia này cũng có trình độ phát triển về công nghiệp và khoa học, đặc biệt là có nền giáo dục đại học hoàn chỉnh, lấy tiếng Anh làm ngôn ngữ chính nên rất thuận lợi về hội nhập.

Báo chí trong nước thường coi Việt Nam và Ấn Độ là 2 nơi có cơ hội tiếp nhận những nhà máy của các nước phát triển khi chúng được di chuyển ra khỏi Trung Quốc. Vấn đề này có đơn giản như vậy chăng? Cứ nhìn vào sự kiện nêu trên về trường hợp Hàn Quốc rút 2 nhà máy vi mạch ra khỏi Trung Quốc để đem sang Ấn Độ, người ta có thể thấy việc chuyển giao công nghệ chế tạo vi mạch từ Liên minh Chip 4 tới Việt Nam thời nay có lẽ không thuận lợi như hơn 20 năm trước nữa: Việt Nam đã bỏ lỡ cơ hội tiếp nhận công nghệ sản xuất vi mạch của Nhật Bản hồi năm 2003 [7].

Sắp tới đây, vì nhu cầu của thời đại về chuyển đổi số [8], Việt Nam không thể không phát triển nền công nghiệp vi mạch. Nhưng xét những hạn chế nêu trên, Việt Nam nên tập trung vào công đoạn Thiết kế chip, và Ứng dụng chip.

Công đoạn thiết kế tự nó đứng biệt lập. Việt Nam đã phát triển thiết kế vi mạch trên hai chục năm nay, nên có thể tiếp tục đi con đường này lên một tầm cao mới. Công tác đào tạo nguồn nhân lực thiết kế vi mạch phải là nhắm tới không những cung ứng cho nhu cầu trong nước mà phải là cả cho nhu cầu nước ngoài. Mục tiêu là trở thành một cái “hub”, một trung tâm thiết kế vi mạch của khu vực và thế giới.

Để làm được như vậy, công tác đào tạo nguồn nhân lực thiết kế từ nay phải là đào tạo “thầy” chứ không phải chỉ là đào tạo “thợ”. Nội dung đào tạo, do đó, phải vượt ra ngoài khuôn khổ “huấn luyện sử dụng đồ nghề hỗ trợ thiết kế - Design Aid Tools”.

Cuối cùng, xin ghi lại đây chút tâm sự kỳ vọng đối với các tốt nghiệp sinh Khóa Training of Trainers (ToT) của SCDC lần này.

Mong các tốt nghiệp sinh của Khóa ToT nỗ lực phát huy năng lực sáng tạo, vươn lên thành các bậc “thầy”, có những đóng góp đột phá trong sự nghiệp phát triển nền công nghiệp bán dẫn vi mạch Việt Nam, chứ không an phận là những “thợ lành nghề,” chỉ tinh thông phép sử dụng công cụ hỗ trợ thiết kế.

Hình 5: Lễ bế giảng khóa Training of Trainers của SCDC.

TÀI LIỆU THAM KHẢO

[1] https://www.youtube.com/watch?v=mxAWgm8r6A.

[2] Nhật đưa Hàn Quốc khỏi 'danh sách trắng' hưởng ưu đãi xuất khẩu - Tuổi Trẻ Online (tuoitre.vn).

[3] https://tuoitre.vn/han-quoc-than-trong-voi-viec-tham-gia-lien-minh-chip-4-20220808131927349.htm

[4] https://viettimes.vn/tai-sao-trung-quoc-lo-ngai-truoc-vien-canh-han-quoc-gia-nhap-lien-minh-chip-do-my-dan-dau-post158985.html.

[5] https://baotintuc.vn/the-gioi/an-do-tren-da-tro-thanh-nen-kinh-te-lon-thu-ba-the-gioi-20220905063009558.htm.

[6] http://www.vietnet24h.vn/kinh-te/samsung-lg-chuyen-co-so-san-xuat-tu-trung-quoc-sang-an-do.

[7] Đặng Lương Mô (2018), Hồi ức tuổi 80 - Hành trình từ điện tử đến vi mạch, Nhà xuất bản Tổng hợp TP Hồ Chí Minh, tr.224-228 và những trang liên quan đến Dự án CMEF (Center for Micro-Electronics Fabrication), ISBN 978-604-58-8437-9.

[8] Đặng Lương Mô (2023), “Vi mạch trong Chuyển đổi Số”, Tạp chí Khoa học và Công nghệ Việt Nam, 1+2, tr.26-30.