Ứng dụng RISC-V trong đào tạo kỹ sư ngành vi mạch bán dẫn

Bài viết đã trình bày theo hệ thống về vai trò chiến lược của kiến trúc vi xử lý RISC-V trong tiến trình tự chủ công nghệ vi mạch tại Việt Nam, đồng thời đề xuất xây dựng, thực hiện một mô hình hệ thống nghiên cứu và phát triển dựa trên nền tảng ESP32-C3.

Ngành vi mạch - bán dẫn đã được Chính phủ xác định là một lĩnh vực chiến lược quốc gia, trong đó việc làm chủ công nghệ vi xử lý giữ vai trò then chốt nhằm bảo đảm năng lực tự chủ và an ninh công nghệ của Việt Nam. Để đạt được mục tiêu này, điều tiên quyết là xây dựng đội ngũ kỹ sư vi mạch - bán dẫn được đào tạo bài bản, gắn liền với thực tiễn.

Tuy nhiên, việc đào tạo đội ngũ kỹ sư vi mạch - bán dẫn hiện naygặp nhiều thách thức khi các kiến trúc vi xử lý độc quyền như ARM hay x86 đều hạn chế quyền tiếp cận công nghệ và bản quyền. Trong bối cảnh đó, kiến trúc mở như RISC-V đang nhận được sự quan tâm của nhiều quốc gia nhờ tính mở, miễn phí bản quyền và khả năng tùy biến linh hoạt. Việc nghiên cứu và thực hành trên nền tảng này không chỉ giúp sinh viên nắm vững nguyên lý, công cụ và quy trình phát triển chip, mà còn góp phần hình thành hệ sinh thái phần cứng - phần mềm mở, tạo nền tảng vững chắc cho mục tiêu làm chủ công nghệ quốc gia.

Bối cảnh chung

Việt Nam đang nổi lên như một trung tâm tiềm năng trong chuỗi cung ứng bán dẫn toàn cầu. Các chính sách quốc gia như Chiến lược phát triển công nghiệp bán dẫn đến năm 2030, tầm nhìn 2045 đã được đề xuất nhằm thúc đẩy năng lực thiết kế vi mạch, phát triển nhân lực và thu hút đầu tư nước ngoài [1]. Tuy nhiên, Việt Nam phải đối mặt với thách thức lớn: phụ thuộc gần như hoàn toàn vào công nghệ sở hữu độc quyền của kiến trúc (ARM, x86) từ các tập đoàn nước ngoài nên rất khó tiếp cận các kiến thức then chốt, cốt lõi của các kiến trúc này.

Trong bối cảnh đó, RISC-V - một nền tảng mở, phi bản quyền cho phép Việt Nam chủ động trong nghiên cứu, thiết kế và đào tạo nhân lực về vi xử lý mà không bị ràng buộc bởi chi phí cấp phép hoặc hạn chế công nghệ. Nền tảng RISC-V là chuẩn mở, công khai toàn bộ đặc tả kiến trúc tập lệnh giúp các trường đại học, viện nghiên cứu dễ dàng tích hợp vào chương trình giảng dạy và nghiên cứu. Điều này tạo ra nền tảng đào tạo thực hành mạnh mẽ, giúp Việt Nam nhanh chóng hình thành đội ngũ kỹ sư thiết kế vi mạch có khả năng tham gia các dự án quốc tế. Nhiều quốc gia như Ấn Độ, Trung Quốc và châu Âu cũng đã triển khai chương trình học RISC-V ở quy mô quốc gia [2].

Việt Nam hoàn toàn có thể học hỏi mô hình này để độc lậptrong một số lĩnh vực quan trọng như:

An ninh - Quốc phòng: Xây dựng vi xử lý an toàn nội địa cho hệ thống thông tin mật, tránh rò rỉ dữ liệu qua phần cứng;

IoT và công nghiệp 4.0: Thiết kế dạng Hệ thống trên chíp (SoC-System on Chip) của RISC-V giúp tiết kiệm năng lượng cho cảm biến, thiết bị đo lường, điều khiển trong sản xuất;

Giáo dục và nghiên cứu: Tạo nền tảng mở cho sinh viên, nhà nghiên cứu phát triển bộ xử lý trung tâm (CPU - Central Processing Unit), bộ xử lý đồ họa (GPU - Graphics Processing Unit)… nội địa;

Chính phủ điện tử và hệ thống nhúng công: Giảm phụ thuộc vào chip nhập khẩu, kiểm soát chuỗi cung ứng phần cứng.

Đặc biệt, trong bối cảnh chuyển đổi số quốc gia, khả năng làm chủ kiến trúc xử lý dữ liệu nội địa là yếu tố cốt lõi để đảm bảo an ninh mạng và chủ quyền công nghệ số.

Mô hình R&D ứng dụng RISC-V trong việc đào tạo nghiên cứu

Trước khi tiến tới mục tiêu làm chủ thiết kế bộ xử lý RISC-V độc lập, giai đoạn đầu nên tập trung khai thác và thử nghiệm trên các nền tảng sẵn có. Hiện nay, trên thị trường có các chíp như PicoRV32, RocketChip, VexRiscvhoặcchíp thương mại (ESP32-C3) đều có kiến trúc RISC-V. Đây có thể coi là một môi trường lý tưởng để nghiên cứu cấu trúc phần cứng - phần mềm, đánh giá hiệu năng và thực hành phát triển ứng dụng. Mô hình R&D ứng dụng các kiến trúc RISC-V sẵn có mang lại nhiều lợi ích cụ thể như: Hiểu sâu nguyên lý chíp CPU, luồng xử lý, bộ điều khiển, bus; Làm quen quy trình thiết kế vi mạch: mô phỏng, tổng hợp, xác minh; Đánh giá hiệu năng, công suất, diện tích trước khi phát triển lõi riêng; Giảm chi phí, tận dụng tài nguyên cộng đồng mã nguồn mở; Phù hợp đào tạo - học thuật, thúc đẩy khởi nghiệp công nghệ bán dẫn.

Mô hình R&D trên giúp rút ngắn thời gian làm chủ công nghệ, hình thành đội ngũ sinh viên, kỹ sư bán dẫn - vi mạch có năng lực thực hành đầy đủ, đảm bảo một nền tảng cho mô hình nghiên cứu và phát triển RISC-V phục vụ đào tạo đại học trong giai đoạn tiếp theo.

Việc lựa chọn thiết bị ESP32-C3 - bộ vi điều khiển Wi-Fi/BLE tích hợp lõi RISC-V 32-bit của hãng Espressif Systems - là một gợi ý cần cân nhắc vì vừa có hiệu năng đủ mạnh cho các bài thí nghiệm, thực hành về các hệ thống nhúng, vừa được hỗ trợ đầy đủ từ nhiều hệ sinh thái phần cứng - phần mềm mở, phù hợp cho triển khai đào tạo tại bậc đại học.

Mô hình nghiên cứu và phát triển dựa trên thiết bị ESP32-C3 có thể cung cấp môi trường thực nghiệm hoàn chỉnh từ cấp độ phần cứng, hệ điều hành thời gian thực, đến lập trình ứng dụng. Bên cạnh đó, thiết bị ESP32-C3 còn cho phép truy xuất và phân tích hoạt động của lõi RISC-V thực trong quá trình vận hành. Ngoài ra thiết bị ESP32-C3 còn tạo nền tảng lý thuyết đầy đủ để thực hiện các giai đoạn mô phỏng, đánh giá hiệu năng, và thử nghiệm thiết kế phần cứng tùy biến (custom extensions) trong tương lai.

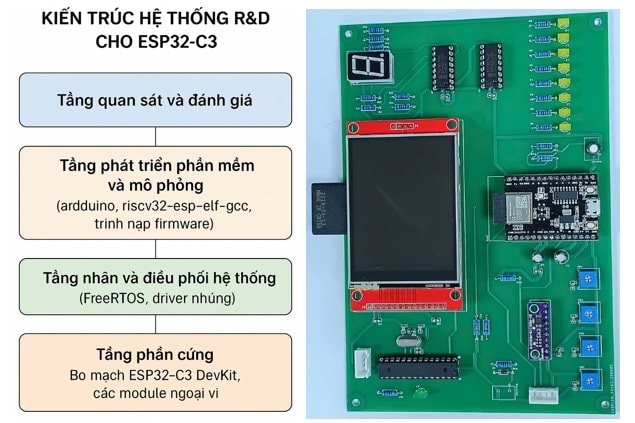

Mô hình nghiên cứu và phát triển dùng thiết bị ESP32-C3 gồm 4 tầng chức năng chính:

Tầng phần cứng (Hardware Platform): gồm bo mạch ESP32-C3 DevKit (lõi RISC-V) và các module ngoại vi tiêu chuẩn: GPIO với đèn Led, nút nhấn, màn hình TFT, thẻ nhớ Sdcard, bàn phím PS2, biến đổi ADC và các giao tiếp UART/SPI/I2C. Phần cứng này có thể mở rộng thông qua bus GPIO hoặc giao diện SPI/I2C cho các thí nghiệm mở rộng về sau.

Tầng nhân và điều phối hệ thống (RTOS & Middleware): sử dụng FreeRTOS và Espressif IDF để quản lý đa nhiệm, đồng bộ dữ liệu, điều khiển thời gian thực, đồng thời tích hợp các thư viện giao tiếp mạng (Wi-Fi/BLE) phục vụ các bài thí nghiệm IoT hoặc giám sát từ xa.

Tầng phát triển phần mềm và mô phỏng (Software & Simulation Environment): bao gồm bộ công cụ biên dịch (arduino, riscv32-esp-elf-gcc), trình nạp firmware (esptool). Hệ thống hoạt động chạy vật lý thực trên phần cứng, cho phép sinh viên đánh giá hiệu năng và hành vi vi kiến trúc.

Tầng quan sát và đánh giá (Monitoring & Analysis): Cung cấp giao diện UART/USB hiển thị dữ liệu thời gian thực (qua Wi-Fi hoặc Serial Plotter). Hỗ trợ người học hiểu sâu, trực quan nội dung thực hành.

Hệ thống R&D cho ESP32-C3 được xây dựng cho phép triển khai chuỗi bài thực hành có tính kế thừa từ cơ bản đến nâng cao, bao gồm:

Lập trình ngoại vi và điều khiển nhúng: thao tác GPIO, UART, PWM, I2C, SPI - giúp hiểu nguyên lý, chức năng các thành phần phần cứng.

Phân tích và mô phỏng pipeline RISC-V: quan sát thực thi lệnh, thời gian xử lý, và ảnh hưởng của cấu trúc pipeline 5-stages.

Thiết kế module tùy biến: Thử nghiệm mở rộng ứng dụng, ghép nối co-processor hoặc FPGA qua các giao tiếp như SPI/I2C để mô phỏng lệnh người dùng định nghĩa (Custom Instructions).

Hệ thống R&D sử dụng ESP32-C3 đem lại những lợi ích cụ thể:

Đào tạo thế hệ kỹ sư thực hành: Sinh viên không chỉ lập trình mà còn hiểu cách vi xử lý hoạt động ở cấp vi kiến trúc;

Thúc đẩy nghiên cứu ứng dụng mở: Nhóm nghiên cứu có thể mở rộng sang mạch tích hợp bán dẫn hoặc thiết kế chip tùy biến;

Cầu nối cho thiết kế chíp RISC-V độc lập: Khi đã thành thạo trên ESP32-3, có thể chuyển sang giai đoạn thiết kế - mô phỏng - chế tạo chip RISC-V “Made in Vietnam”.

Trong giai đoạn tiếp theo, hệ thống có thể mở rộng theo hướng đồng mô phỏng phần mềm - phần cứng và tích hợp nền tảng học trực tuyến, cho phép sinh viên truy cập và thực hành RISC-V từ xa qua mạng, phù hợp với mô hình đào tạo đại học hiện đại.

Có thể nói việc khai thác các nền tảng RISC-V thương mại sẵn có mang lại cơ hội hiện thực để đào tạo, thử nghiệm và chuyển giao công nghệ một cách chủ động, tiết kiệm chi phí, thời gian nhưng vẫn bảo đảm tính thực tiễn và mở rộng. Thông qua mô hình đề xuất, các hoạt động nghiên cứu có thể được triển khai từ cấp độ vi mô (kiến trúc tập lệnh, pipeline, tối ưu hóa mã máy) đến cấp độ hệ thống (FreeRTOS, giao tiếp ngoại vi, kết nối mạng, và ứng dụng IoT). Đây cũng là hướng đi được kỳ vọng phù hợp để hình thành chuỗi nghiên cứu - đào tạo - sản xuất thử nghiệm, đồng bộ trong lĩnh vực đào tạo bán dẫn - vi mạch.

Trong giai đoạn tiếp theo, việc mở rộng hệ thống theo hướng tích hợp FPGA, mô phỏng SoC RISC-V tự thiết kế, cũng như xây dựng phòng thí nghiệm mở (open lab) sẽ là bước tiến quan trọng nhằm thúc đẩy năng lực tự chủ về thiết kế và sản xuất chip trong nước.

Nền tảng RISC-V không chỉ là công cụ học tập, mà còn là nền tảng công nghệ chiến lược góp phần hiện thực hóa mục tiêu phát triển công nghiệp bán dẫn Việt Nam đến năm 2030 và tầm nhìn 2045.

Tài liệu tham khảo

[1] Bộ Thông tin và Truyền thông Việt Nam (2024), Chiến lược phát triển công nghiệp bán dẫn Việt Nam đến năm 2030, tầm nhìn 2045.

[2] RISC-V International (2023), “Global Adoption Programs and Academic Initiatives,” https://riscv.org/blog/risc-v-international-newsletter-december-2023/, truy cập ngày 03/11/2025.